# THD Minimization of 3-Phase Voltage in Five Level Cascaded H-Bridge Inverter

Mrs. Sarika D Patil<sup>1</sup>, Sumant G Kadwane<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering Rajiv Gandhi College of Engineering & Research Nagpur, India <sup>2</sup>Department of Electrical Engineering Yeshwantrao Chavan College of Engineering Nagpur, India

**Abstract**: In this paper, the analysis of Selective Harmonic Elimination (SHE) for 3-Phase Voltage Source Inverter (VSI) is presented. Investigation harmonics which are produced by Pulse Width Modulation (PWM) technique is necessary as it affects the system parameters. Higher order harmonics are easily eliminated by choosing a proper tuned value filters but lower order harmonics such as 3rd, 5th, 7th, and 9th are not eliminated easily. This paper presents optimization method for SHE reduction i.e. Newton Raphson Method with random initial guess and shows the various feasible regions where the solution can exit by solving transcendental non linear equations. .By using this method lower order harmonics as well as Total Harmonic Distortion (THD) will also reduce. In this paper a cascaded 3-Phase, 5- Level, H-bridge Multilevel Inverter using MATLAB/Simulink blocks is presented as a systematic approach for developing the model.

**Keywords**: Flexible AC Transmission System, Multilevel Inverter, Power Electronics, Selective Harmonic Elimination, SPWM-Sinusoidal Pulse Width Modulation

## I. Introduction

Recently Multilevel Inverters are widely used in many industrial applications, where the requirement is medium voltage and high power applications. Multilevel Inverter has been widely used for chemical, oil, and liquefied natural gas plants, water plants, marine propulsion, power generation, energy transmission, and powerquality devices, FACTS Devices [1-3]. Cascaded H-bridge converter topology is prominently used and particularly useful for renewable energy and DSTATCOM applications [4-5], [9]. While in comparison with traditional two-level voltage source inverters, multilevel inverters have several advantages. The main advantage of multilevel inverter is that of its stepwise output voltage. This advantage results in higher power quality, lower switching losses, higher voltage capability moreover it also reduces the cost with transformer less system at the distribution side. It has low distortion, low dV/dt and can draw input current with very low distortion, can generate smaller common mode voltage, thus reducing the stress in the motor bearings in motor applications, and also it can operate with a lower switching frequency. Desired output can be obtained from multilevel inverter with several number of dc voltages as inputs. If the number of levels is increased the output voltage and current waveform approaches to the sinusoidal waveform. The different topologies, control strategies and modulation techniques used for Multilevel inverters have been presented in [6-7]. Reference [8] elaborates the industrial applications of multilevel inverter. Consequently the reduced switching methods with lower computation cycles are investigated in [10].

The generalized formulation of Selective Harmonic Elimination of multilevel inverter is presented in literature recently. Half wave symmetry SHE PWM formulation is presented in [11-14], which describes the formulation of SHE problem based on lower harmonic elimination technique. The generalized problem for SHE is presented in various papers and nonlinear equations with advanced computing methods like genetic algorithm, particle swarm optimization, bee algorithm and bacterial foraging [13-17]. These papers primarily focus on the method of solving the nonlinear equations with the exact formulation of SHE problem with MATLAB/Simulink. resent paper attempts to formulate the in depth MATLAB/Simulink based simulation of SHE problem with optimization algorithm that will help the new researchers to carry out the research for further investigating new SHE algorithms by spending less time in modeling the SHE problem.

## II. Review Of Generalized She For Multilevel Inverter

The A multilevel cascade inverter consists a number of H-bridge cells that are connected in series per phase, and each module requires a separate DC source to generate voltage levels at the output of inverter.

$$V_{out} = \begin{cases} V_{dc} & In_1, In_4 ON \\ 0 & In_1, In_3 ON \\ V_{dc} & In_2, In_3 ON \end{cases}$$

(1)

The switching inputs shown as  $S_i$ , i=1 to 4 in the Fig. 1 allows obtaining output voltage as per (1). The Hbridge cells are serially connected over AC outputs to obtain expanded phase voltage levels and therefore, the total output level is the synthesize of cells output of each H-bridge. Cascade Multilevel Inverter (CMLI) is one of the most important topology in the family of multilevel and multipulse inverters.

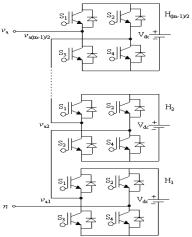

Fig.1 Cascaded H-Bridge Multilevel Inverter

It requires least number of components as compared to diode-clamped and flying capacitors. The minimum number of levels and the voltage rating of the active devices (IGBTs, GTOs, power MOSFETs, etc.) are inversely related to each other. More levels in the inverter will lower the required voltage device rating of individual devices; or looking at it another way, a higher voltage rating of the devices will enable a fewer minimum number of levels to be used. The cascaded multilevel inverter consists of a number of H-bridge inverter units with separate dc source for each unit and is connected in cascade or series as shown in Fig. 1.

The output voltage levels as seen from Fig. 2 of each phase and each line voltage is given by (2) and (3) respectively.

| m = 2s + 1                    | (2) |

|-------------------------------|-----|

| Switching devices $= 2(m-1)$  | (3) |

| DC Bus capacitors = $(m-1)/2$ |     |

where 's' is the number of bridges, 'm' is the number of levels. The ratio of DC voltage source naturally affects the output levels of a cascade multilevel inverter. The Fourier series expansion of the general multilevel stepped output voltage is given in (4), where n is the harmonic number of the output voltage of inverter.  $V(wt) = \sum_{n=1}^{\infty} Vn \sin(nwt)$  (4)

Where

Fig. 2 Output voltage waveform of 7-level Cascaded Multilevel Inverter

The switching angles can be chosen to obtain minimum voltage harmonics. Normally, these angles are chosen so as to cancel the predominant lower frequency harmonics. The selective harmonic elimination method is also called fundamental switching frequency method based on the harmonic elimination theory proposed in [18],[19]. The major difficulty for selective harmonic elimination methods, including the fundamental switching

frequency method and the Virtual Stage PWM method, is to solve the transcendental equations for switching angles.

To satisfy fundamental voltage and to eliminate 5th and 7th harmonics, three nonlinear equations are as follows.

$$V_{1} = \frac{4 \text{Vdc}}{\pi} [\cos(\theta_{1}) + \cos(\theta_{2}) + \cos(\theta_{3})] = V_{1}^{*}$$

(5)

$$V_{5} = \frac{4 \text{Vdc}}{5\pi} [\cos(5\theta_{1}) + \cos(5\theta_{2}) + \cos(5\theta_{3})] = 0$$

(6)

$$V_{7} = \frac{4 \text{Vdc}}{7\pi} [\cos(7\theta_{1}) + \cos(7\theta_{2}) + \cos(7\theta_{3})] = 0$$

(7)

Subject to  $0 < \theta_{1} < \theta_{2} < \theta_{3} < \frac{\pi}{2}$

These equations are nonlinear transcendental equations are solved by Newton-Raphson method using Random Initial Guess, as the solution doesn't depend upon the guess. This paper presents a multilevel inverter model with mathematical model for SPWM modulator to minimize THD.

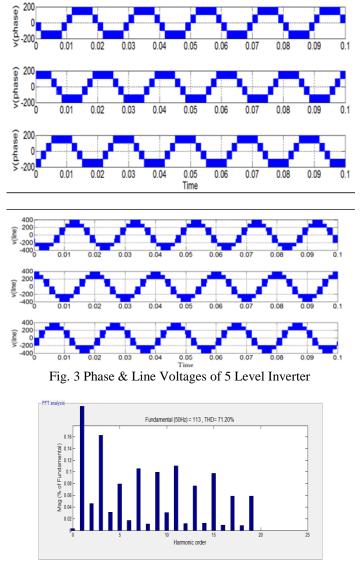

#### III. Description Of Model For Case Study Of 5-Level Inverter

The primary building blocks in MatLab can be divided into 3 subsystems namely: Generation of gate pulses, simulation of 5-level inverter by spwm method, minimization of harmonics and THD by selective harmonic elimination method. The Reference sine wave is generated sine block with 120° displacement for each phase and amplitude as per the modulation index requirement. Fig. 3 shows the phase and line voltage of 5-level multilevel inverter whereas Fig.4 shows the FFT analysis showing Total THD of 71.20% by SPWM method.

Fig. 4 FFT Analysis by SPWM Method

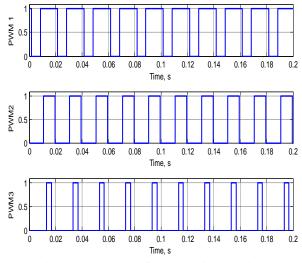

#### IV. Selective Harmonic Elimination Method

These offline calculated constant values of firing angles are then compared with the sine wave through comparator and given to gate pulses of respective switches(IGBT) in H- Bridge Model. For three phase generation the angles are displaced by  $120^{\circ}$  in each phase. The corresponding system for generating firing pulses is shown in Fig. 5. The dead band is not considered in this simulation model and complementary pulse is fed to the upper and lower switches of each leg of H bridge inverter. Here sine wave is compared with firing angle

Fig. 5 PWM Pulses for generating H bridge

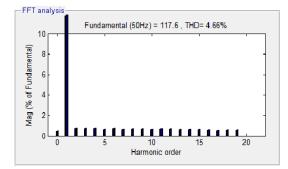

By inserting notches at a particular instant, total THD is reduced to 4.66% which is below IEEE 519 standard as shown in Fig.6

Fig. 6 FFT Analysis for Selective Harmonic Elimination (SHE)

|          | Harmonic                                       | FFT Analysis of | Total Harmonic |

|----------|------------------------------------------------|-----------------|----------------|

| S.<br>No | Elimination                                    | Magnitude (% of | Distortion     |

|          | Techniques                                     | fundamental)    | (THD)          |

| 1        | Sinusoidal PWM                                 |                 |                |

|          | Technique                                      | 113.3           | 71.20          |

| 2        | Selective Harmonic<br>Elimination<br>Technique | 117.6           | 4.66%          |

## V. Filter Section

Here LC filter is used to filter out the ripple and minimize the higher order harmonics In LC filter an Inductor is connected in series with the load (RL). It offers high resistance path to The load (RL). The capacitor transverse the load through the inductance, In this manner the AC component are filtered and a flat

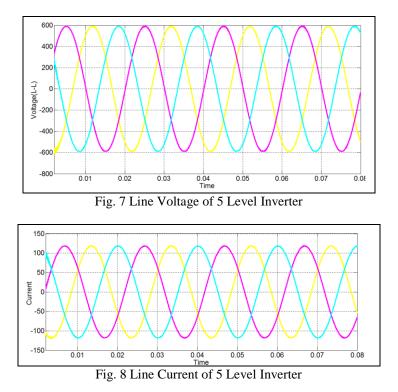

DC is supplied all the way through the load. Here the distorted harmonics are removed and the smooth wave forms are obtained .Here the distorted harmonics are removed and the smooth wave forms are obtained as shown in Fig. 7 & 8.

#### VI. Conclusion

Simulation of Multilevel Inverter for three phase 5-Level inverter with SHE in MATLAB/Simulink is presented as a systematic design approach. The results obtained from simulation of MATLAB/Simulink shows that the harmonic THD contents are 4.66% and also third, fifth and seventh harmonics are within 1% tolerance.  $9^{\text{th}}$  harmonic shall be automatically cancelled and other higher order harmonics are eliminated by filter. While it is to be noted that the fundamental harmonic is preserved and selected order of harmonics are very small which strongly confirms the validity of proposed system.

#### References

- J. S. Lai, F. Z. Peng, Multilevel Converter-A New Breed of Power Converters, IEEE Trans. Industry Applications, Vol. 32, No. 3, May/June 1996, pp. 509-517.

- L.M.Tolbert, F.Z.Peng, Multilevel Converters as a utility interface for renewable energy system, IEEE conference, 2000 Vol.2, pp. 1271-1274.

- [3]. T.A. Meynard, H. Foch, P. Thomas, J. Courault, R. Jakob, and M. Nahrstaedt, Multicell Converters: Basic concepts and Industry applications, IEEE Trans on Industrial Application, Vol.49, No. 5, pp 955-964, Oct.2002.

- K. Corzine, Y. Familiant, A new cascaded multilevel H-bridge drive, IEEE Trans on Power Electron., Vol. 17, No. 1, pp. 125–131, Jan. 2002.

- [5]. N. Farokhnia, S. H. Fathi, and H. R. Toodeji, Direct nonlinear control for individual DC voltage balancing in cascaded multilevel DSTATCOM, in Proc. IEEE Int. Conf. EPECS, 2009, pp. 1–8.

- [6]. J. Rodriguez, J.S. lai, and F.Z. Peng, Multilevel Inverters: A Survey of topologies, controls, and applications, IEEE Trans on Industrial Electronics, Vol. 49, No. 4, pp 724-738, Aug 2002.

- [7]. L.G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillio, and M.A. M. Prats, The age of multilevel Converters arrives, IEEE Trans on Industrial Electronics., Mag, Vol.2, No. 2, pp 28-39, June 2008.

- [8]. S.Kouro, M. Malinowski, K Gopakumar, J. Pou, L.G. Franquelo, Wu Bin, J Rodriguez, M.A Perez, J.I.Leon, Recent Advances and Industrial Electronics, Vol 57, Issue: 8, Page(s): 2553 – 2580, 2010.

- [9]. Mariusz Malinowski, K. Gopakumar, Jose Rodriguez, Marcelo A. Perez, A Survey on Cascaded Multilevel Inverters, IEEE Trans on Industrial Electronics., Vol. 57, No. 7, July 2010.

- [10]. Applications of Multilevel Converters, IEEE Trans on Industrial Electronics, Vol 57, Issue: 8, Page(s): 2553 2580, 2010.

- [11]. L.G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillio, and M.A. M. Prats, The age of multilevel Converters arrives, IEEE Transon Industrial Electronics., Mag, Vol.2, No. 2, pp 28-39, June 2008.

- [12]. S.Kouro, M. Malinowski, K Gopakumar, J. Pou, L.G. Franquelo, Wu Bin, J Rodriguez, M.A Perez, J.I.Leon, Recent Advances and Industrial Applications of Multilevel Converters, IEEE Trans on Industrial Electronics, Vol 57, Issue: 8, Page(s): 2553 – 2580, 2010.

- [13]. Mariusz Malinowski, K. Gopakumar, Jose Rodriguez, Marcelo A. Perez, A Survey on Cascaded Multilevel Inverters, IEEE Trans on Industrial Electronics., Vol. 57, No. 7, July 2010.

- [14]. Samir Kouro, Jaime Rebolledo, Jose Rodriguez, Reduced Switching Frequency-Modulation Algorithm for High-Power Multilevel Inverters, IEEE Transactions On Industrial Electronics, Vol. 54, No. 5, October 2007.

- [15]. Mehrdad Tarafdar Hagh, Hassan Taghizadeh, Kaveh Razi ,Harmonic Minimization in Multilevel Inverters Using Modified Species-Based particle Swarm Optimization, IEEE Transactions On Power Electronics, Vol. 24, No. 10, October 2009.

- [16]. Ayoub Kavousi, Behrooz Vahidi, Reza Salehi, Mohammad Kazem Bakhshizadeh, Naeem Farokhnia, S. Hamid Fathi, Application of the Bee Algorithm for Selective Harmonic Elimination Strategy in Multilevel Inverters, IEEE Trans on Power Electronics, Vol. 27, No. 4, APRIL 2012.

- [17]. R.N. Ray, D. Chatterjee, S.K. Goswami, Reduction of voltage harmonics using optimisation- based combined approach, IET Power Electronics IET Power Electron., Vol. 3, Iss. 3, pp.334–344,2010.

- [18]. H. S. Patel, R. G. Hoft, Generalized Harmonic Elimination and Voltage Control in Thyristor Converters: Part I harmonic elimination, IEEE Transactions on Industry Applications, vol. 9, pp. 310-317. May/June 1973.

- [19]. H. S. Patel, R. G. Hoft, Generalized Harmonic Elimination and Voltage Control in Thyristor Converters: Part II –Voltage Control Technique, IEEE Transactions on Industry Applications, vol. 10, pp. 666-673.Sept./Oct. 1974,